四位加法器REPORT

郭高旭 ggx21@mails.tsinghua.edu.cn 2021010803

实验目的

-

掌握组合逻辑电路的基本分析方法与设计方法;

-

理解半加器、全加器、加法器的分析与设计方法;

-

学会元件例化;

-

学会利用软件仿真实现对数字电路的验证与分析

实验内容

-

设计半加器

-

利用半加器构建全加器

-

使用全加器构造逐次进位加法器,超前进位加法器

-

使用 VHDL自带的加法运算实现一个 4 位全加器

-

查看逐次进位加法器、超前进位加法器和 VHDL 自带加法器在CPLD中生成的电路,并比较这三者的异同

不同加法器的RTL与仿真结果

超前进位加法器

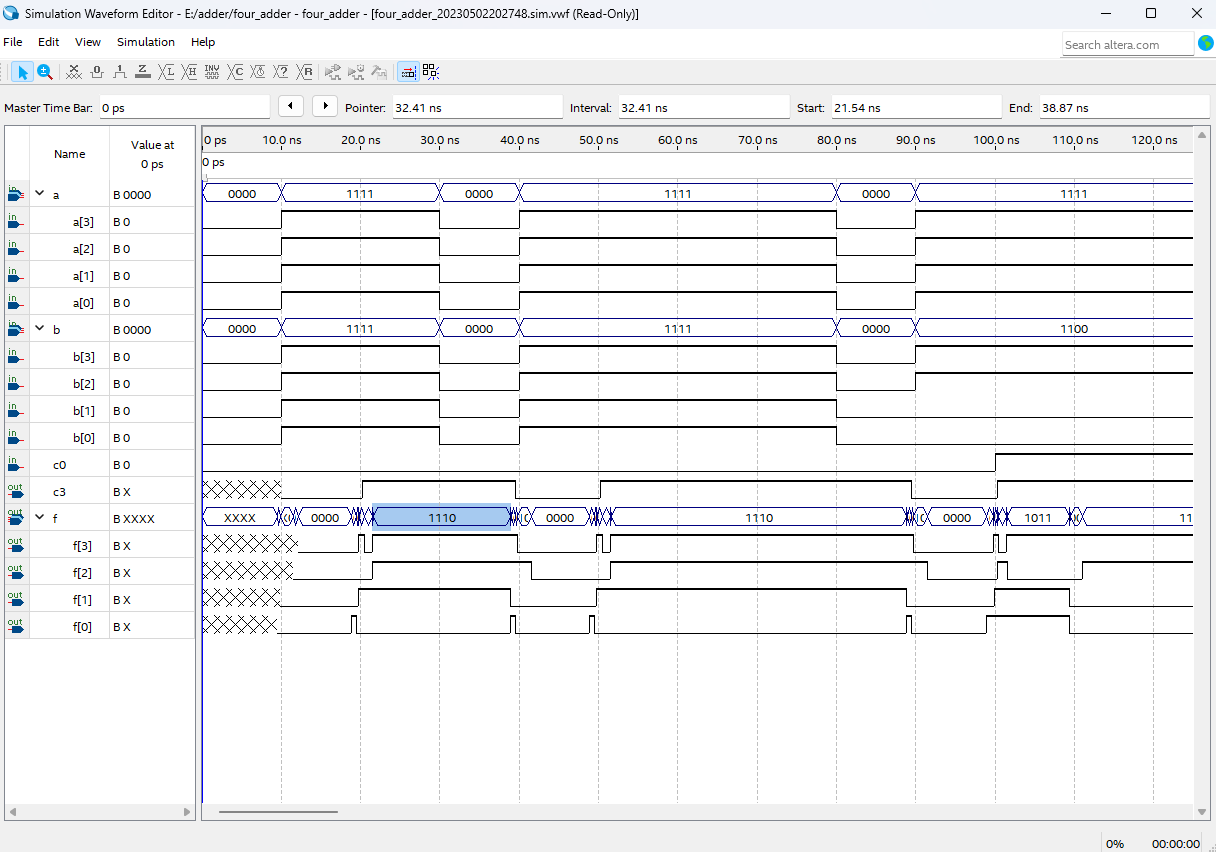

仿真结果

超前进位加法器延迟:End-Start=17.33ns

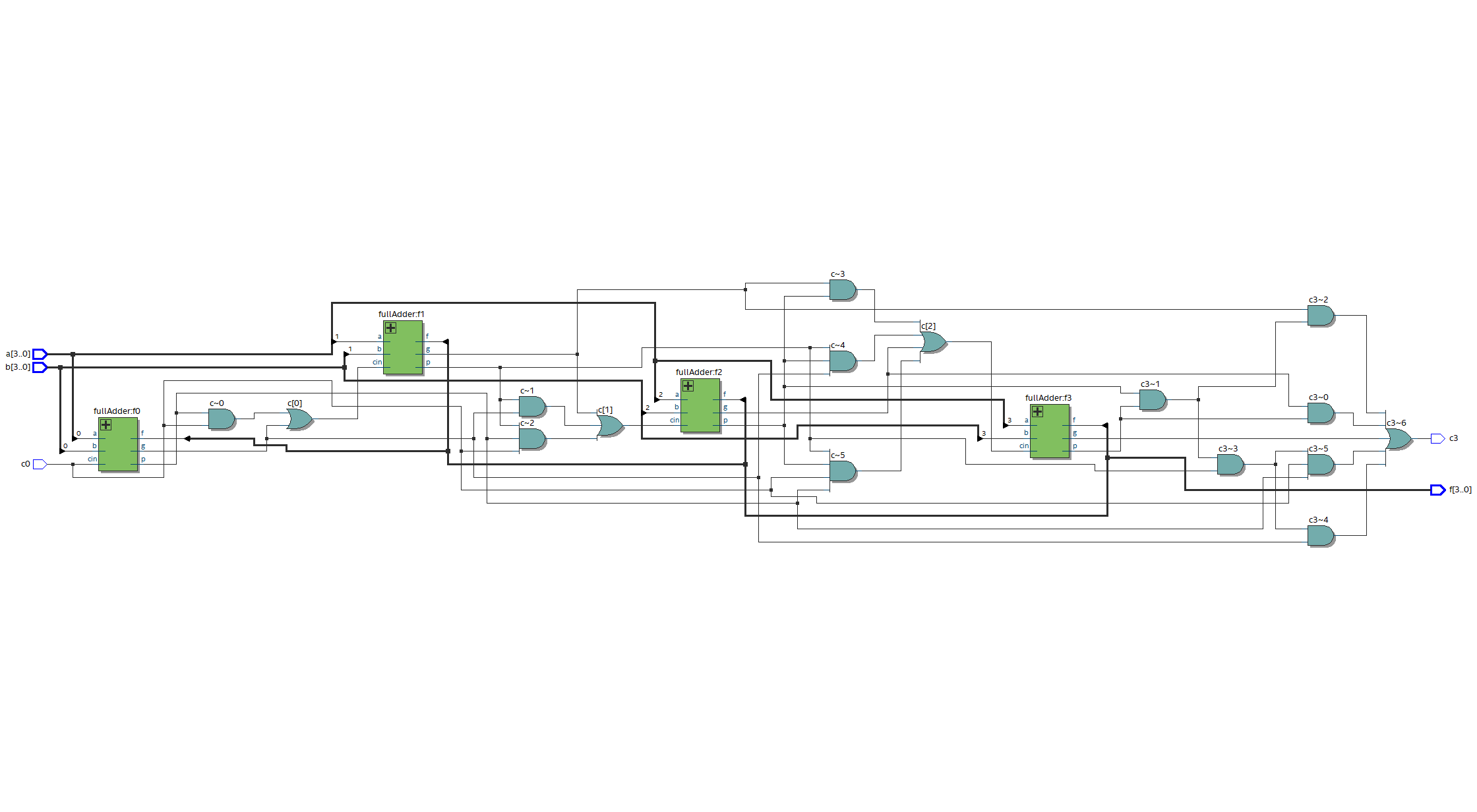

RTL

简单进位加法器

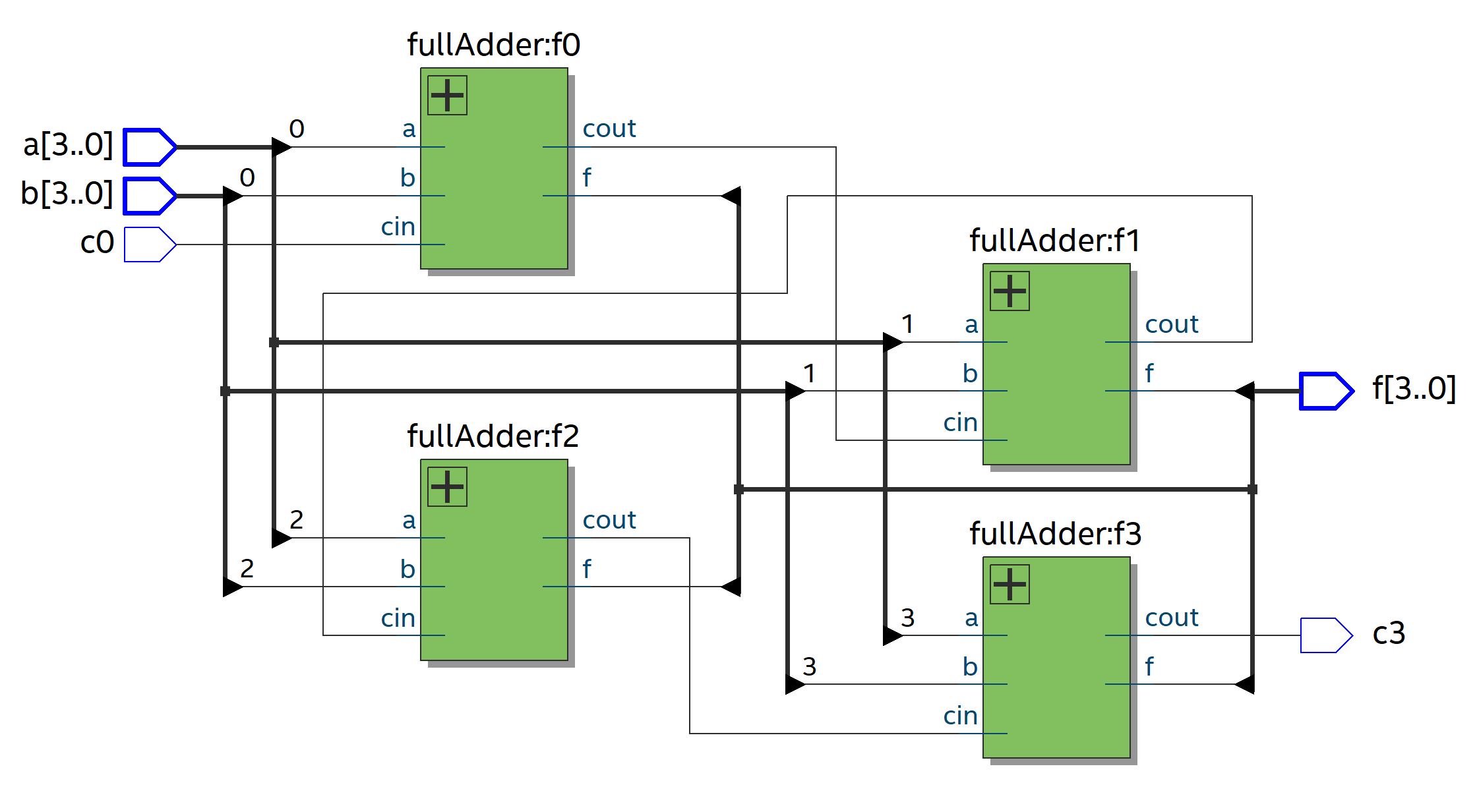

RTL

##### 仿真结果

##### 仿真结果

超前进位加法器延迟:End-Start=17.96ns

原生加法器

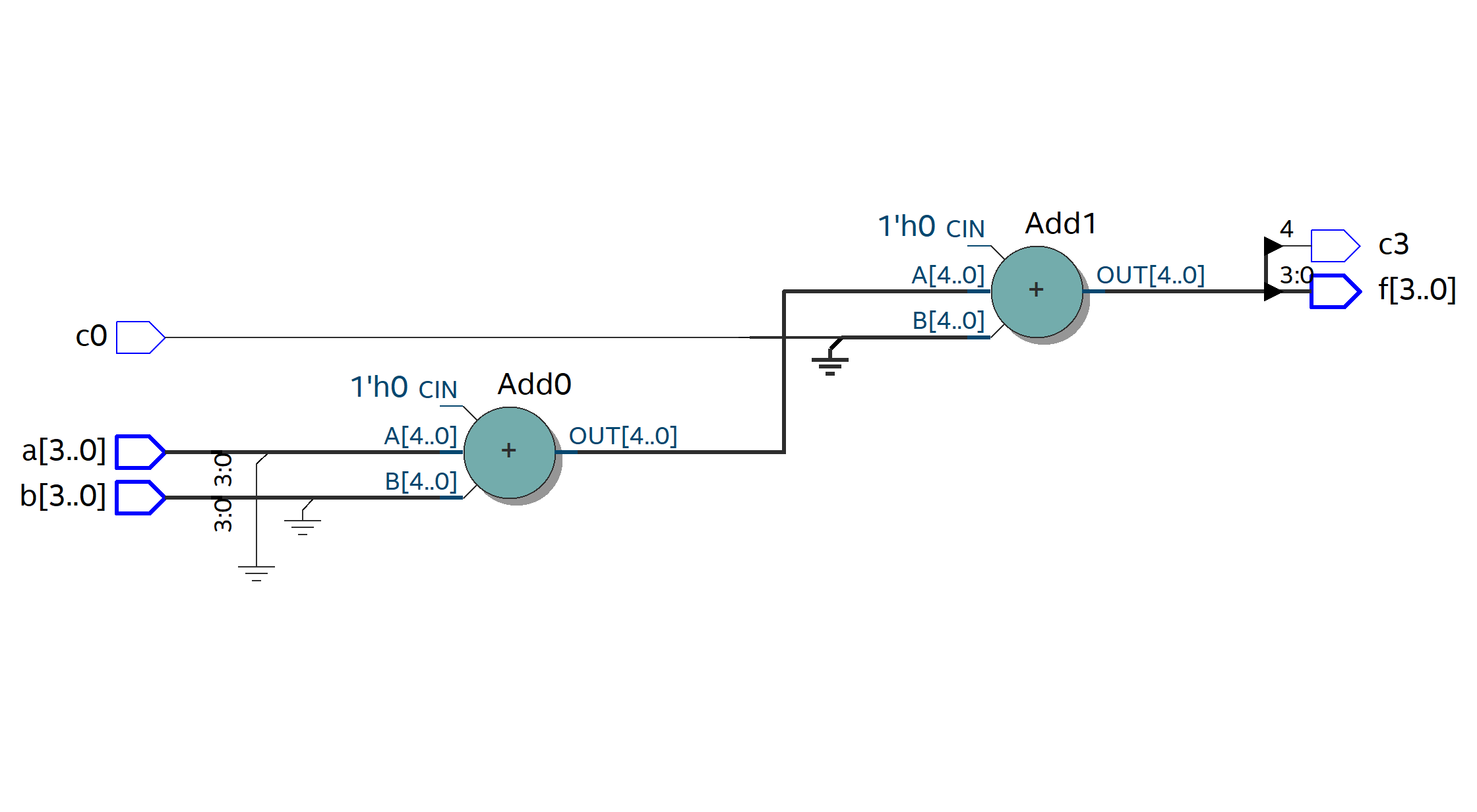

RTL

代码

1 | LIBRARY ieee; |

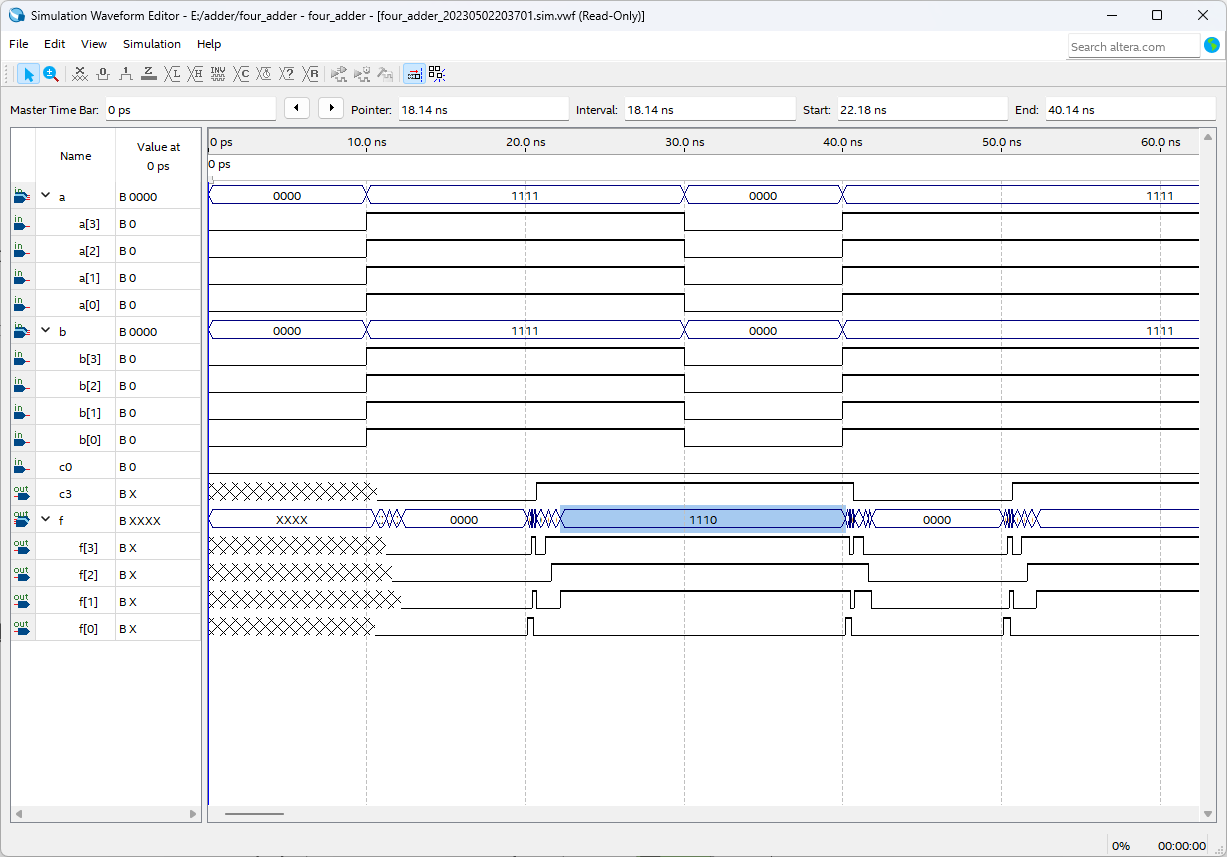

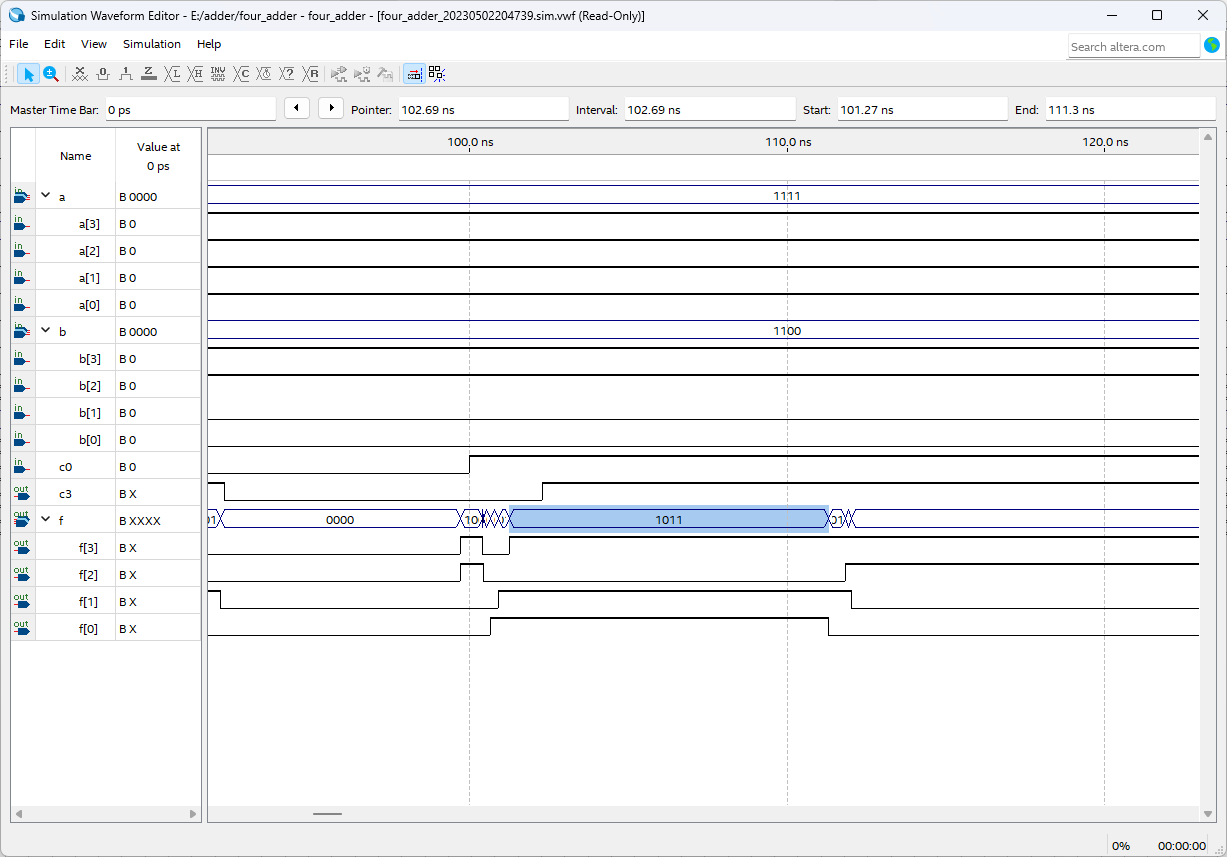

仿真结果

原生加法器延时:10.03ns

总结:

我实现的超前进位加法器比普通进位加法器延迟略小。但原生加法器延时远小于我实现的。

电路功能测试的结果

-

实际功能测试结果从计算结果上来说和仿真测试结果相同

-

实验时的延迟效果几乎都无法感知

调试中遇到的问题

-

对仿真操作不够熟悉,在学习仿真时花费了很多时间。